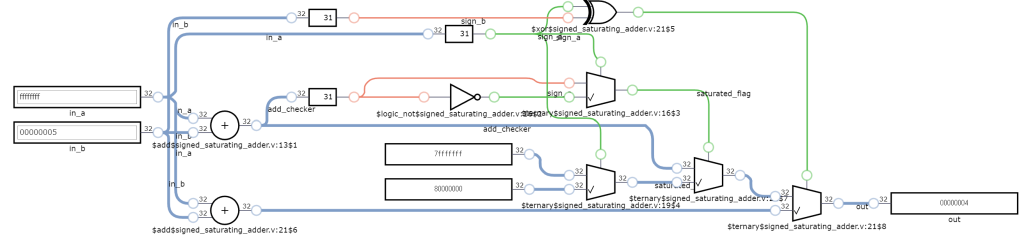

[Verilog] 飽和符号対応加算器

概要

- 2入力、符号対応(入力の最上位ビットが正負を表す)、加算時の飽和対応の加算器

- 入出力データ幅はパラメータ化

- モジュール内にレジスタなし

ソース

Module

module signed_saturating_adder #(

parameter DATA_WIDTH = 32

)(

input [DATA_WIDTH - 1:0] in_a,

input [DATA_WIDTH - 1:0] in_b,

output [DATA_WIDTH - 1:0] out

);

wire sign_a, sign_b;

assign sign_a = in_a[DATA_WIDTH - 1];

assign sign_b = in_b[DATA_WIDTH - 1];

wire [DATA_WIDTH:0] add_checker;

assign add_checker = {sign_a, in_a} + {sign_b, in_b};

wire saturated_flag;

assign saturated_flag = (sign_a)? !add_checker[DATA_WIDTH - 1]: add_checker[DATA_WIDTH - 1];

wire [DATA_WIDTH - 1:0] saturated_value;

assign saturated_value = (sign_a)? {1'b1, {(DATA_WIDTH - 1){1'b0}}}:{1'b0, {(DATA_WIDTH - 1){1'b1}}};

assign out = (sign_a ^ sign_b)? in_a + in_b : (saturated_flag)? saturated_value:add_checker[DATA_WIDTH - 1:0];

endmodule

テストベンチなどはこちら: https://edaplayground.com/x/VMLd

プログラミング風景を動画にしました

ディスカッション

コメント一覧

まだ、コメントがありません